Rambus has just unveiled an industry-first, complete memory interface chipset for Gen5 DDR5 RDIMMs and next-gen DDR5 MRDIMMs.

VIEW GALLERY – 2 IMAGES

The company says that these innovative new products for RDIMMs and MRDIMMs “will seamlessly extend DDR5 performance with unparalleled bandwidth and memory capacity for compute-intensive data center and AI workloads”.

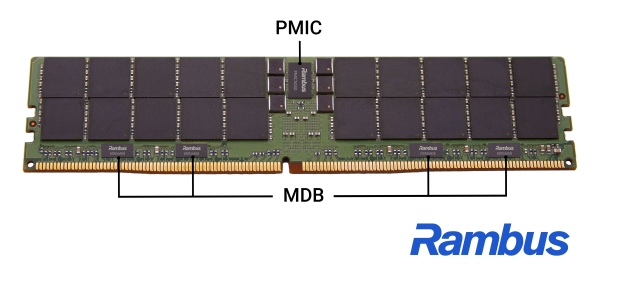

Rambus’ says that its new Gen5 DDR5 chipset enables flexible and scalable end-user server configuration, with its DDR5 RDIMM 8000 and industry-standard MRDIMM 12800 utilize a common architecture and compatibility across server platforms. The DDR5 RDIMM 8000 chipset includes the Gen5 RCD, PMIC5030, Serial Presence Detect (SPD) Hub and Temperature Sensor (TS) chips. The DDR5 MRDIMM 12800 chipset includes the MRCD and MDB, as well as the same PMIC5030, SPD Hub and TS chips utilized in the RDIMM 8000.

Sean Fan, chief operating officer at Rambus said: “The voracious memory demands of AI and HPC require the relentless pursuit of higher performance through continued innovation and technology leadership. With our 30-plus years of renowned high-speed signal integrity and memory system expertise, the Rambus Gen5 RCD, and next-generation MRCD, MDB, and PMIC will be critical enabling chips in future-generation servers leveraging DDR5 RDIMM 8000 and MRDIMM 12800“.

The new Rambus chips include:

- The Gen5 Registering Clock Driver (RCD) , enabling RDIMMs operating at 8000 megatransfers per second (MT/s).

- The Multiplexed Registering Clock Driver (MRCD) and Multiplexed Data Buffer (MDB) , enabling upcoming MRDIMMs running at speeds up to 12,800 MT/s by doubling the bandwidth of the DIMM beyond the native DRAM device speed.

- The second-generation server Power Management IC (PMIC5030) designed for both DDR5 RDIMM 8000 and MRDIMM 12800, providing ultra-high current at low voltage to support higher speeds and more DRAM and logic chips per module.