While the new CAMM and LPCAMM memory modules for laptops have garnered a great deal of attention in recent months, it’s not just the mobile side of the PC memory industry that is looking at changes. The desktop memory market is also coming due for some upgrades to further improve DIMM performance, in the form of a new DIMM variety called the Clocked Unbuffered DIMM (CUDIMM). And while this memory isn’t in use quite yet, several memory vendors had their initial CUDIMM products on display at this year’s Computex trade show, offering a glimpse into the future of desktop memory.

A variation on traditional Unbuffered DIMMs (UDIMMs), Clocked UDIMMs (and Clocked SODIMMs) have been created as another solution to the ongoing signal integrity challenges presented by DDR5 memory. DDR5 allows for rather speedy transfer rates with removable (and easily installed) DIMMs, but further performance increases are running up against the laws of physics when it comes to the electrical challenges of supporting memory on a stick – particularly with so many capacity/performance combinations like we see today. And while those challenges aren’t insurmountable, if DDR5 (and eventually, DDR6) are to keep increasing in speed, some changes appear to be needed to produce more electrically robust DIMMs, which is giving rise to the CUDIMM.

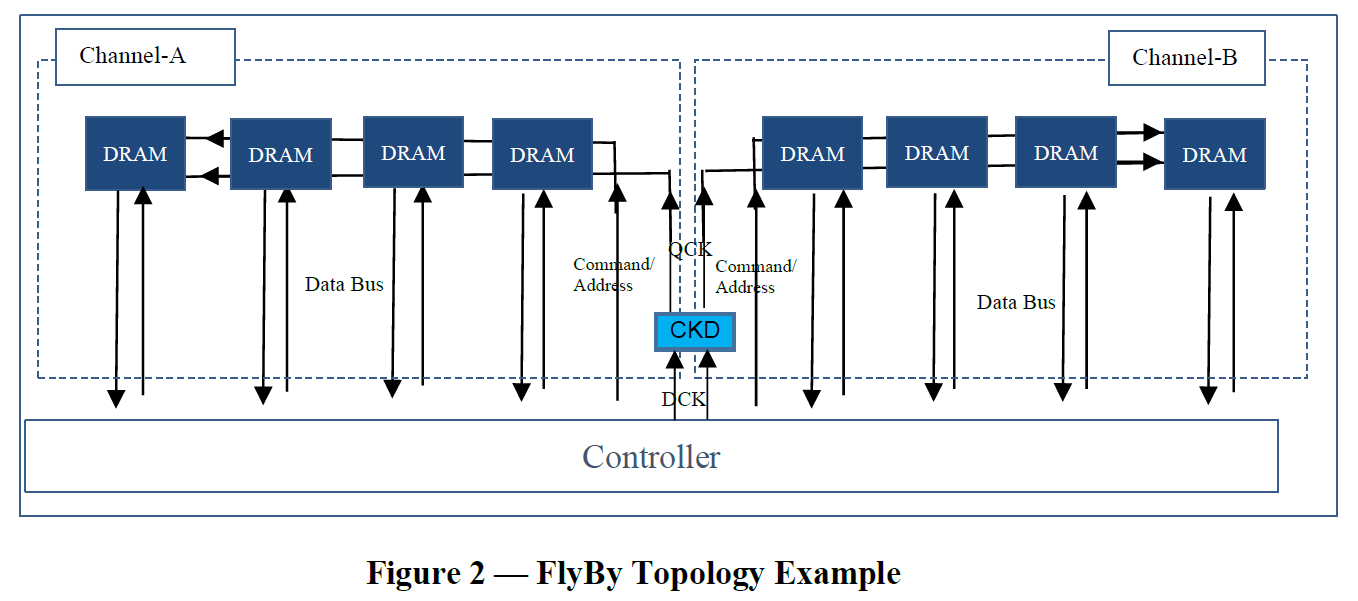

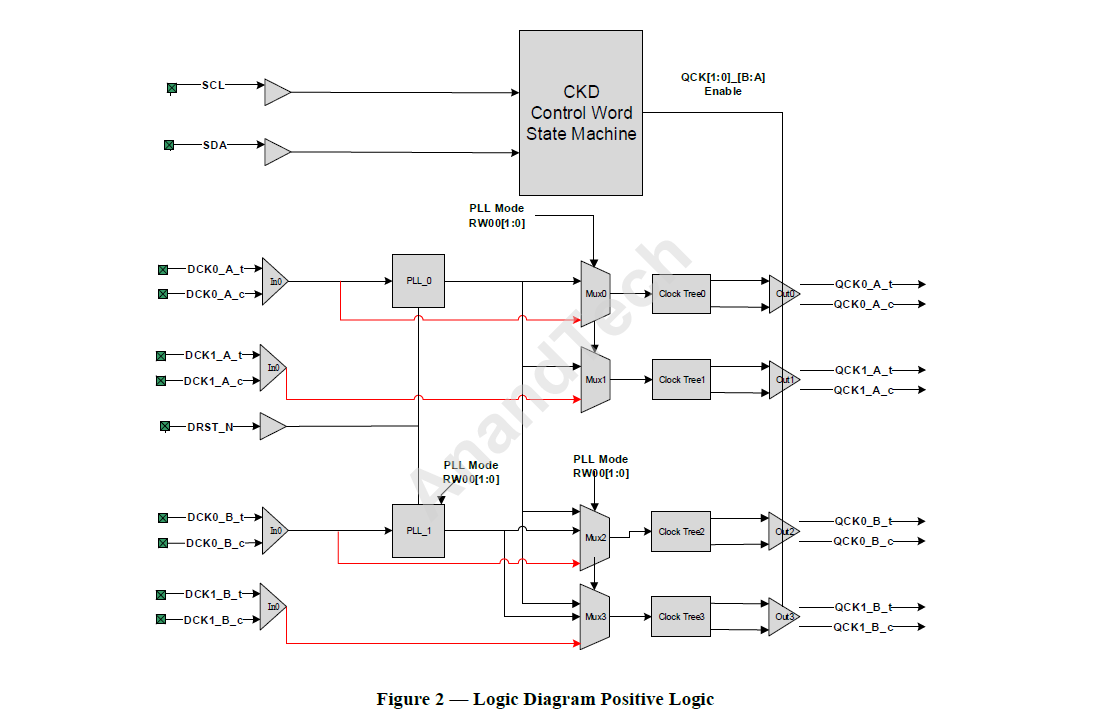

Standardized by JEDEC earlier this year as JESD323, CUDIMMs tweak the traditional unbuffered DIMM by adding a clock driver (CKD) to the DIMM itself, with the tiny IC responsible for regenerating the clock signal driving the actual memory chips. By generating a clean clock locally on the DIMM (rather than directly using the clock from the CPU, as is the case today), CUDIMMs are designed to offer improved stability and reliability at high memory speeds, combating the electrical issues that would otherwise cause reliability issues at faster memory speeds. In other words, adding a clock driver is the key to keeping DDR5 operating reliably at high clockspeeds.

All told, JEDEC is proposing that CUDIMMs be used for DDR5-6400 speeds and higher, with the first version of the specification covering speeds up to DDR5-7200. The new DIMMs will also be drop-in compatible with existing platforms (at least on paper), using the same 288-pin connector as today’s standard DDR5 UDIMM and allowing for a relatively smooth transition towards higher DDR5 clockspeeds.

CUDIMMs: The Key To Faster DDR5

As outlined above, one of the biggest challenges for highly-clocked memory subsystems today is maintaining signal integrity, particularly over relatively long distances and with multiple interconnections (e.g. multiple DIMMs per channel). Traditionally, the weight of this task has primarily fallen on the memory controller/CPU, and to a lesser extent the motherboard, as UDIMMs are relatively dumb devices on their own. But with CUDIMMs, that paradigm is set to change by making DIMMs just a bit smarter, and thus making them capable of helping out with maintaining signal integrity.

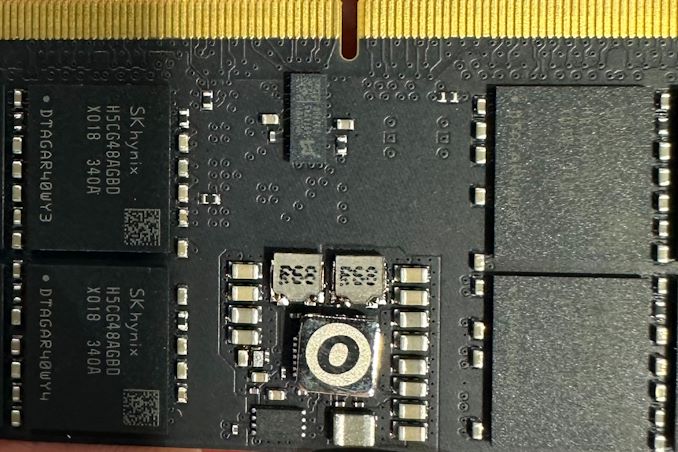

The big change here is the addition of a clock driver (CKD), which receives a base clock signal and regenerates it to redistribute to memory components on the module. A CKD essentially buffers the incoming clock signal, and then amplifies it on the way out when it drives the clock signal to the memory chips on the DIMM. CKDs also incorporate signal conditioning features such as duty cycle correction, which allows for for accurate timing and jitter reduction, and minimizing the overall rapid variations in the clock signal’s timing.

Minimizing clock skew – the difference in arrival times of the clock signal at different components – is another key function of the CKD. By matching propagation delays for each clock path, the CKD can ensure memory chips (and DIMMs) remain fully synchronized.

CSODIMM with Montage’s 1st Gen CKD Clock Driver (Upper Center)

Meanwhile, phase adjustment capabilities allow CKD to align the clock signal with the specific timing needs of different components, which means some additional work on the memory module maker’s side. Which is perhaps why we have not seen many memory module vendors demonstrating their CKD-enabled products today as they still need to get familiar with the technology.

This figure is reproduced, with permission, from JEDEC document JESD323, figure 2

All told, placing clock drivers in DIMMs isn’t a new idea; the CUDIMM concept is largely a scaled-down version of the Registered DIMM (RDIMM), which has been used in servers for years and is the only type of DDR5 DIMM that Intel and AMD’s server (and workstation) chips support. But whereas RDIMMs are a more expansive solution that buffers the command and address busses alongside the clock signal, CUDIMMs buffer only the clock signal and leave everything else untouched. In that context, CUDIMMs are essentially a half-step to RDIMMs.

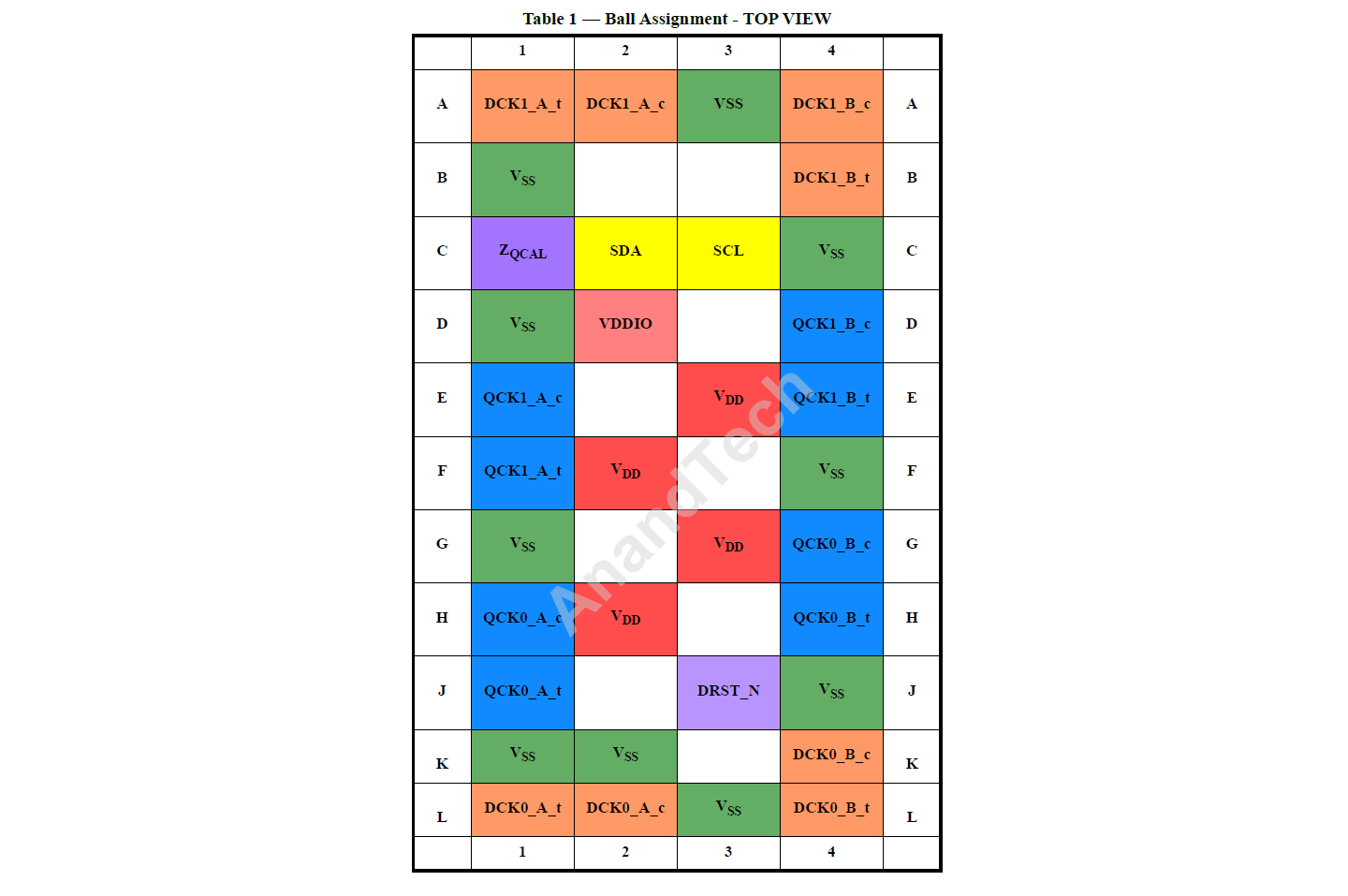

And while there are some CPU designers out there that would no doubt be ecstatic if all systems used RDIMMs (and ECC, as well), the economics of consumer PCs favors cheaper and less complex solutions when they’re available. The design of the CKD itself reflects this; a JEDEC-standard CKD is just 35 pins, and nearly half of those are merely voltage/ground pins. So while CKDs represent an additional cost for DIMM construction, they are rather purposely designed to be cheaper to build than RDIMMs.

This figure is reproduced, with permission, from JEDEC document JESD82-531A.01, Table 1

In any case, CKDs will be coming to all of JEDEC’s DDR5 memory form factors. So along with the CUDIMM, we’ll have the Clocked SODIMM (CSODIMM), and even DDR5 CAMM2 memory modules will use clock drivers.

Though since the need (or at least, standardization) around clocked DIMMs is based on the memory frequency, CUDIMMs and their other variations are all designed to be backwards compatible with existing DDR5 systems and memory controllers. Which means that a CUDIMM will use the same 288-pin DIMM slot as standard DDR5 DIMMs.

This figure is reproduced, with permission, from JEDEC document JESD82-531A.01, Figure 2

Under the hood, this is accomplished by allowing a CUDIMM to either run a clock signal though the buffers on its CKD, or bypass those buffers entirely, running in the aptly named PLL Bypass mode. Officially, bypass mode is only supported for speeds up to DDR5-6000 (3000MHz), so JEDEC complaint DIMMs will be expecting to use CKD mode (Single PLL or Dual PLL) at DDR5-6400 and beyond. The end result being that a CUDIMM should work with a slower/older DDR5 memory controller by going into bypass mode, whereas DIMMs without a CKD won’t be available at the higher speeds that require a CKD (not at JEDEC-standard voltages and timings, at least).

CUDIMMs and CSODIMMs at Computex

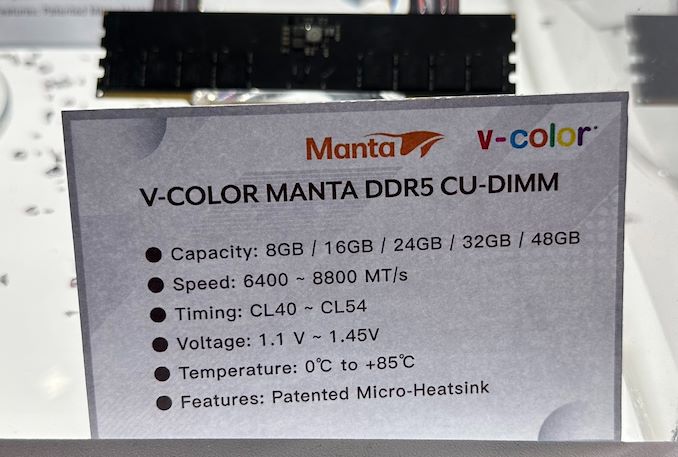

Several memory vendors, including G.Skill, TeamGroup, and V-Color, had CUDIMMs and CSODIMMs on display at Computex. Given that these new DIMMs go hand-in-hand with new platforms, the memory vendors aren’t talking too much about specifics here. But since they had the hardware on display, don’t be too surprised if we see them go into production systems (and retail shelves) sooner than later.

Biwin is a relatively new name on the market of enthusiast-grade memory modules (as previously the company sold high-performance devices under the Acer Predator brand, and still does, so to speak). But it enters the game with advanced 16 GB and 32 GB modules rated for 6400 – 8800 MT/s operation, which is higher compared to ‘regular’ enthusiast-grade DIMMs . These devices are set to be available in September.

G.Skill, which has been a major enthusiast memory vendor for ages, demonstrated its Trident Z5 CK CUDIMMs at Computex as well. Though the company did not really highlight their performance, perhaps because it is still polishing off its CKD-enabled products and they are not yet setting records. At the end of the day, G.Skill has showcased a heavily overclocked system running at DDR5-10600 using regular DDR5 modules, so early CUDIMMs are not quite as eye-catching in comparison.

By contrast, TeamGroup demonstrated its DDR5-7200 memory modules with a CKD chip at the trade show.

Finally, unlike some of its rivals, V-Color seems to be taking some serious advantage of CKD chips for high-performance memory offerings, as it showcased both CUDIMMs and CSODIMMs at the trade show. The company is planning to offer 16GB and 24 GB CUDIMMs with speed bins between 6400 MT/s and 9000 MT/s at 1.1 V – 1.45 V. 9000 MT/s is faster than any easily-attainable enthusiast-class memory kits available today, so this is meant to highlight advantages of clock unbuffered memory modules.

There are many suppliers of high-performance memory modules and yet only four of them demonstrated their CUDIMMs at Computex. Of those, only two decided to talk about expected performance of CUDIMMs (TeamGroup’s demonstration looks like a work-in-progress type of thing). Though with the JEDEC standard having been on the books for almost half a year now, they will no doubt soon be joined by the myriad of other memory vendors that call the PC market home.